LDO模擬集成電路設計 從原理到實踐

LDO(Low Dropout Regulator,低壓差線性穩壓器)是模擬集成電路設計中一類至關重要的電源管理器件,廣泛應用于各類電子系統中,為敏感電路提供穩定、低噪聲的供電電壓。其設計融合了模擬集成電路設計的核心思想與針對特定功能的優化策略。

1. LDO的基本工作原理與核心指標

LDO本質上是一個負反饋系統。其基本結構通常包含誤差放大器(EA)、功率調整管(Pass Transistor,通常為PMOS或PNP型)、反饋電阻網絡以及負載。誤差放大器持續比較反饋電壓(由輸出電壓分壓得到)與基準電壓(Bandgap Reference)的差值,并通過驅動功率調整管來調整其導通狀態,從而穩定輸出電壓。

LDO的關鍵性能指標包括:

- 壓差電壓(Dropout Voltage):維持規定穩壓精度時,輸入與輸出電壓之間的最小差值。低壓差是現代LDO的核心優勢,尤其適用于電池供電場景。

- 靜態電流(Quiescent Current, IQ):LDO自身工作所消耗的電流,直接影響系統待機時間。低IQ設計是便攜設備的關鍵。

- 負載調整率(Load Regulation):負載電流變化時輸出電壓的穩定能力。

- 線性調整率(Line Regulation):輸入電壓變化時輸出電壓的穩定能力。

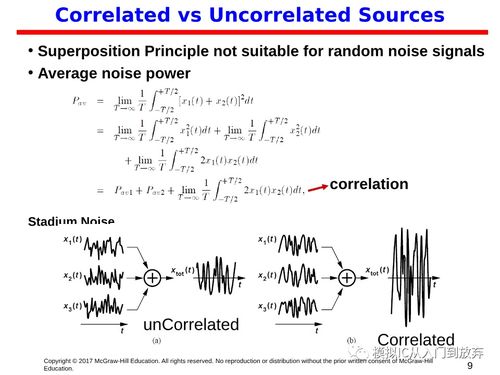

- 電源抑制比(PSRR):衡量LDO抑制輸入電源紋波和噪聲的能力,對于射頻、音頻等敏感電路至關重要。

- 瞬態響應(Transient Response):負載電流發生階躍變化時,輸出電壓的過沖/下沖及恢復時間。

2. LDO設計的核心挑戰與電路技術

LDO設計并非簡單的誤差放大與調整,它面臨一系列相互制約的挑戰:

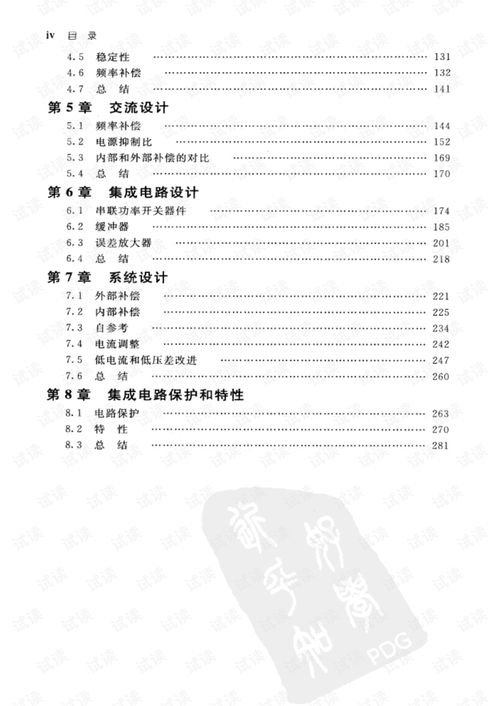

穩定性與補償:LDO是一個條件穩定系統。其環路穩定性受輸出電容(包括ESR)、負載電流大小等因素的顯著影響。為確保在全負載范圍和溫度下穩定,必須采用精密的補償技術。常見的補償方法包括:

- 主極點補償:在誤差放大器輸出端(即功率管柵極)形成主極點。

- 米勒補償:利用功率管本身的米勒電容進行補償,能有效節省面積。

- 前饋補償:在反饋網絡中引入零點,以抵消輸出極點的影響,改善瞬態響應。

功率管設計:作為電流通路的核心,功率管的選擇(PMOS vs. PNP)和尺寸設計直接影響壓差、驅動能力、瞬態響應和芯片面積。PMOS功率管因其易于集成和低驅動電流需求而更常見于CMOS工藝中。

基準源與誤差放大器:一個高精度、低溫度漂移的帶隙基準電壓源是LDO性能的基礎。誤差放大器則需要高增益、高PSRR和足夠的擺幅,其架構(如折疊式共源共柵、兩級運放等)需根據整體性能折中選擇。

瞬態響應優化:快速的瞬態響應需要環路具有高帶寬,但這與穩定性要求相沖突。設計師常采用額外的瞬態增強電路,如采用輔助的快速通路(Slew-Rate Enhancement Circuit)或動態偏置技術,在負載跳變時瞬間提供或吸收大電流,以最小化輸出電壓波動。

無電容LDO(Capacitor-Less LDO):為節省外部元件成本和PCB面積,無電容LDO成為研究熱點。它通過創新的內部補償和頻率響應整形技術,在不依賴外部大電容ESR的情況下實現穩定,但通常對設計復雜度和工藝變化更敏感。

3. LDO在整體集成電路設計流程中的位置

LDO設計是典型的模擬/混合信號IP設計流程:

- 指標定義:根據系統需求(如輸入/輸出電壓范圍、最大負載電流、靜態功耗預算、PSRR要求等)確定設計規格。

- 架構選擇:基于工藝和指標,確定整體架構(如是否采用無電容結構、補償方案、功率管類型)。

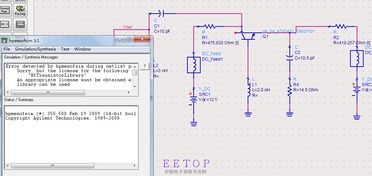

- 電路設計與仿真:使用EDA工具(如Cadence Virtuoso)進行晶體管級設計,并通過仿真(DC、AC、瞬態、蒙特卡洛、PVT角仿真)驗證各項指標。

- 版圖設計:考慮匹配、噪聲、電流密度、ESD、latch-up等因素進行物理實現。功率管的布局、走線寬度(承受大電流)和散熱設計尤為關鍵。

- 后仿真與驗證:提取版圖寄生參數后,再次進行全面的仿真驗證,確保性能達標。

- 流片與測試:交付給晶圓廠制造,隨后進行硅片測試,驗證實際性能。

4. 發展趨勢

隨著工藝節點不斷進步和系統級封裝(SiP)的普及,LDO設計正朝著以下方向發展:

- 超低功耗與高能效:適應物聯網設備的需求,靜態電流已可低至數十納安。

- 高集成度:作為電源管理單元(PMU)的一部分,與DCDC轉換器、充電管理等模塊集成。

- 數字化輔助與自適應:引入簡單的數字電路(如輕負載檢測、環路參數自適應調整)以優化不同工作狀態下的性能。

- 先進工藝下的挑戰:在納米級CMOS工藝下,電源電壓降低,晶體管閾值電壓未同比縮放,給設計高精度、低壓差LDO帶來新挑戰。

###

LDO模擬集成電路設計是理論與實踐深度結合的典范。它要求設計師深刻理解反饋控制理論、半導體器件物理、工藝特性以及系統應用需求,并在性能、面積、功耗和成本之間做出精妙的權衡。一個優秀的LDO設計,不僅僅是電路原理圖的實現,更是對穩定性、魯棒性和實用性的全方位考量,是模擬集成電路設計智慧的集中體現。

如若轉載,請注明出處:http://m.fuiun.cn/product/13.html

更新時間:2026-03-07 18:12:29